Applications:

|

|

Features:

|

|

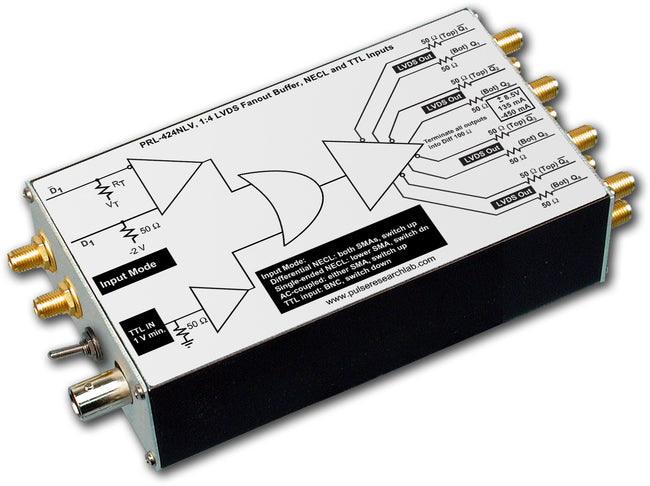

DescriptionThe PRL-424NLV is a 1:4 fanout, complementary output, LVDS line driver. It is intended for converting NECL signals, AC-coupled sine waves, or TTL signals into multiple LVDS signals for driving long lines. The PRL-424LV high speed fanout line driver facilitates testing of high speed digital communications circuits and distribution of satellite signals. The PRL-424NLV has two logically ORed input circuits:

The four pairs of complementary outputs are 50 Ω back-terminated and are designed for driving floating 100 Ω loads, normally the configuration used in LVDS input circuits. The output swing is typically 600 mV with a common mode voltage of 1.2 V. All output connectors are SMA. The PRL-424NLV is supplied with a ±8.5 V/1.8 A AC/DC adapter and housed in a 1.3 x 2.9 x 5-in. extruded aluminum enclosure. Available accessories include voltage distribution modules and brackets for mounting multiple units. (1) A related model, the PRL-424LV, has a "universal differential" input (floating 100 Ω termination) that will accept LVDS, RS-422, NECL and LVPECL, so long as the NECL and LVPECL signals are differential and have internal pull-down resistors. |

Fig. PRL-424NLV Block Diagram

Fig. PRL-424NLV Block Diagram