Applications:

|

|

Features:

|

|

DescriptionThe PRL-350LP is a ready-to-use, high speed dual-channel comparator module. The PRL-350LP has a maximum clock frequency in excess of 300 MHz and has complementary LVPECL outputs designed for driving 50 Ω transmission lines terminated to 50 Ω/+1.3 V. Both channels have DC coupled 50 Ω inputs and outputs. The input threshold voltage can be selected either from a set of preset values of -50 mV, 0 V or +50 mV using a common three-position switch. The input Common Mode Range is -2.0 V to +3.0 V.

These high speed comparators are Mini Modular Instruments ™ that can be used as peak detectors, threshold detectors, sine wave to square wave converters, window comparators or differential line receivers, etc. Typical minimum input voltage required at 300 MHz is 10 mVPP into 50 Ω. Each unit is supplied with a ±8.5 V AC/DC Adapter and housed in an attractive 1.3 x 2.9 x 3.9-in. extruded aluminum enclosure. |

*For the PRL-350LP, an unused complementary output must be either terminated into 50 Ω/+1.3 V or AC-coupled into a 50 Ω load; otherwise, output waveform distortion and rise time degradation will occur.

Use the PRL-550LPQ4X, four channel LVPECL Terminator for the 50 Ω/+1.3 V termination and for connection of LVPECL signals to 50 Ω input oscilloscopes.

Anritsu Application Note for PON Module Testing with Anritsu MP1800A

Signal Quality Analyzer and PRL-350 Series Comparators (1.1 MB PDF)

BERT Level Translation

Anritsu engineers and customers around the world rely on our PRL-350 Series comparators for level conversion when testing Passive Optical Network (PON) modules.

PON module testing often requires converting the -1.0 to 0 V signals output by the MU181020A Pulse Pattern Generator cards to the LVTTL, PECL or LVPECL levels required by many ONU and OLT modules, typically for the Data, Pre-bias, and Reset signals.

Popular models include:

- PRL-350TTL-NIM, Dual Channel Comparator with TTL Outputs

- PRL-350LP-NIM, Dual Channel Comparator with LVPECL Outputs

- PRL-350P, Dual Channel Comparator with PECL Outputs

App Note and block diagram copyright and courtesy of Anritsu Corporation.

(0° C ≤ TA ≤ 35° C)*

Unless otherwise specified, dynamic measurements are made with all outputs terminated into 50 Ω/VTT, where VTT = -2 V for ECL outputs and 0 V for TTL outputs.

td align="center" nowrap="nowrap">V td align="center" nowrap="nowrap">ns td align="center" nowrap="nowrap">| Symbol | Parameter | PRL-350LP | Unit | ||

|---|---|---|---|---|---|

| Min | Typ | Max | |||

| RIN | Input Resistance | 49.5 | 50.0 | 50.5 | Ω |

| ROUT | Output Resistance | 49.5 | 50.0 | 50.5 | Ω |

| VTH+ | Preset positive threshold voltage | 49.5 | 50.0 | 50.5 | mV |

| VTH- | Preset negative threshold voltage | -50.5 | -50.0 | -49.5 | mV |

| VTH0 | Preset zero threshold voltage(1) | -10 | 0 | 10 | mV |

| VOL | Output Low Level | 1.5 | 1.7 | 1.8 | V |

| VOH | Output High Level | 2.3 | 2.5 | 2.7 | V |

| IDC+ | DC Input Current, +8.5 VDC | 175 | 200 | mA | |

| IDC- | DC Input Current, -8.5 VDC | -325 | -350 | mA | |

| VDC+ | DC Input Voltage | +7.5 | +8.5 | +12 | V |

| VDC- | DC Input Voltage | -12 | -8.5 | -7.5 | V |

| VAC1 | AC/DC Adapter Input Voltage, 120 VAC | 103 | 115 | 127 | |

| VAC2 | AC/DC Adapter Input Voltage, 220 VAC | 206 | 230 | 254 | |

| tPLH | Propagation Delay to output↑ | 1.8 | ns | ||

| tPHL | Propagation Delay to output↓ | 1.8 | |||

| tr/tf | Rise/Fall Times(2) | 1100 | 1250 | ps | |

| tSKEW | Skew between any 2 outputs | 750 | 1000 | ps | |

| Vin I | Minimum Input Voltage @ 150 MHz(3) | 20 | 10 | mVPP | |

| Vin II | Minimum Input Voltage @ 250 MHz(3) | 20 | 10 | mVPP | |

| VCM | Input Common Mode Range | -2.0 | +3.0 | V | |

| fmax | Max. Clock Frequency(4) | 300 | 330 | MHz | |

| Size | 1.3 x 2.9 x 3.9 | in. | |||

| Weight, w/o AC adapter | 7 | Oz | |||

| Shipping weight, w/AC adapter | 4 | lb | |||

(1) If the switch is set to the center position (0 V threshold) a non-driven channel will oscillate and induce jitter in the driven channel. Connect any output to any input to stop the oscillation.

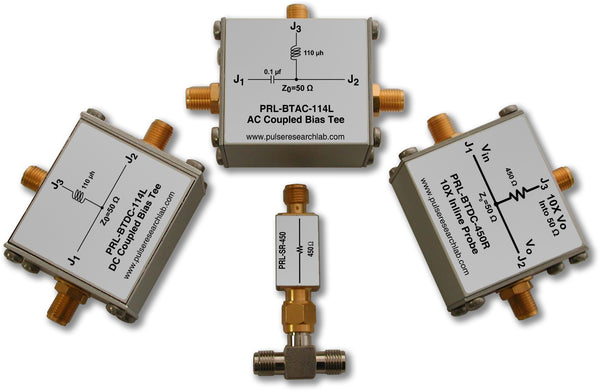

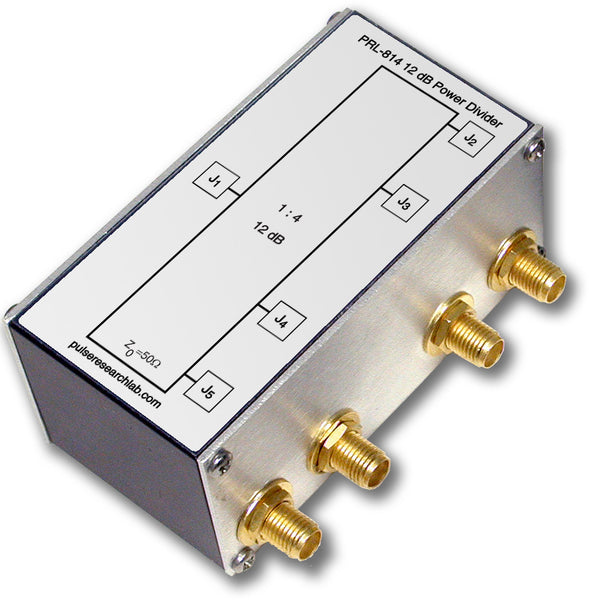

(2) 20%-80% for LVPECL. For the PRL-350LP, an unused complementary output must be either terminated into 50 Ω/VTT or AC coupled into a 50 Ω load; otherwise, output waveform distortion and rise time degradation will occur. Use the PRL-ACT-50 Dual Channel AC-Coupled 50 Ω Termination for terminating unused complementary outputs. Use the PRL-550LPQ4X, four channel LVPECL Terminator for the 50 Ω/VTT termination and for connection of LVPECL signals to 50 Ω input oscilloscopes. If preservation of DC levels is not required, then the PRL-SC-104A, 0.1 µf DC block or a 12 dB AC-coupled attenuator may be used to connect the LVPECL outputs to 50 Ω input instruments.

(3) In order to reduce jitter near fMAX, terminate the non-driven input into 50 Ω when the input voltage is less than 20 mVPP.